# 総括ロードマップ技術指標(ORTC)

# 背景

総括ロードマップ技術指標(ORTC: Overall Roadmap Technology Characteristics) の表は、国際技術ワーキンググループ(ITWG)が詳細に章を執筆する活動のための叩き台として、ロードマップ作成過程の初期に利用される。これらの表は、ロードマップ更新作業を行うに当たって特定表間の不整合を強調し、技術ワーキンググループ(TWG)間での整合をとる手段としても使用される。表を改訂する作業では、基本となる傾向モデルを開発して目標値の同意を得るために、ITWG や各 TWG 間で様々なレベルでの調整およびコンセンサス(合意)形成を行なう。この結果、ORTC表は数回の反復と審査の過程を経ることになる。

ORTC 表にはメートル標記の数値が記載され、ロードマップ全体を通して各ワーキンググループの章にはさらに詳しく記載されている。本節に記載される情報は、現在の半導体技術進歩の急速な進展を強調することを目的としている。この情報は 2004 年に開始した改訂と更新作業の集大成となっている。 なお ORTC 用語集が付録として載せられている。

# 2005年改訂の概要

# 定義

上で述べたとおり、ロードマップ全体の技術的特長の表に主要技術数値が要約されている。特定の行項目について特に指定しない限り、デフォルトの年ヘッダーでは、(以前のロードマップと同じく)製造サイトからの「生産装置」を使った製品出荷量が、1万ユニット/月・ICを最初に越えた年を示している。更に3ヶ月以内に2番目の会社が生産を開始することが必要である(Figure3参照のこと)。ASIC【Application Specific IC:特定用途向け集積回路】では、この定義を満たすため、装置で処理した多数の個別製品系列項目の累積量を用いても良い。

ITRS のエグゼクティブ・サマリーの紹介で述べられているが、再度繰り返して言うと、各社の「ノード」の進展とタイミングの一般プレス発表には、引き続き混乱がある。この「ノード」は ITRS の定義と目標に合致しているものもあり、していないものもある。2003 年版 ITRS を作成している時には、多くのロジック製造会社が行った、2003年に製造された「90nm」技術「ノード」と言及している一般プレス発表を調停する試みが行われた。実際のデバイスのコンタクト有りメタル 1(M1)ハーフピッチは 110-120nm と述べられており、ITRS DRAM 千鳥コンタクト有りM1 ハーフピッチのヘッダー目標との関係に関して混乱が持ち上がっていた。先進の製造会社と会話した後、公で述べているもののあるものは(密度に関して)ハーフピッチと(スピード性能に関して)露光ゲート長の平均を表して指標化した技術ノード・ロードマップを述べていることが分かった。ある会社は製品の機能が 2 倍になる(例として、ロジックゲート数やメモリ・ビット数が 2 倍になる)タイミングを述べていた。技術の進歩を計るこのアプローチは「ノード」の関係を複雑なものにした。と言うのは、密度の改善は設計の改善とリソのリニヤな像寸法縮小で達成されるからである。

更なる混乱が、Flash メモリ製品の発表で技術「ノード」が言及された事により起こった。Flash 技術は 2005 年版 ITRS で強調されて述べられている。例えば、Flash の製品セル密度はコンタクトなしポリシリコン(ポリ)配線ハーフピッチで決まっており、メタル 1(M1)ハーフピッチ(DRAM、MPU、ASIC 製品で密度を決めている鍵となるパターン)によって決まっていない。また、非常に挑戦的な Flash メモリ・セルのセルエリアファクター(用語集参照のこと)改善が、果敢にコストを削減し、急速に立ち上がる不揮発性メモリ(NVM)の需要を満たすために、Flash セル設計者によって行われている。

#### 2 総括ロードマップ技術指標 (ORTC)

国際ロードマップ委員会(IRC)は、2005 年末に ITRS と個々の会社の公的発表の間の混乱を最小限にする最善の方法は、様々な技術傾向のドライバーを製品で、すなわち DRAM, MPU/ASIC、Flash で分けることであると決断した。前に述べたように、MPU/ASICと DRAM 製品のハーフピッチは今や両者とも M1 千鳥コンタクト有りで言及されており、他方、Flash 不揮発性メモリ(NVM)製品はコンタクトなしポリの高密度ライン(Figure2 参照)で言及されている。表のヘッダーの選択を簡単にするために、MPU のコンタクト無しハーフピッチ・ラインは 2005年版 ITRS には含まれていない。個々の TWG 表は夫々の表で技術の傾向ドライバーを最も代表するヘッダーライン項目を採用している。

別々の製品傾向を追跡することを新たに強調するため、「hp X X」「ノード」の言及(即ち、hp90, hp65, hp45 等 DRAM 製品 M1 ハーフピッチにのみ関連しているもの)は 2005 年版 ITRS から共通の表へッダーより取り去った。 2005 年版 ITRS では、個々の製品グループ(DRAM, Flash, ASIC)に付随した、技術の傾向、機能(トランジスター数、ビット数、ロジックゲート数) や特徴(スピード、電力)性能が強調されている。 ITRS と比較をしたい個々の会社は、いまや言及する製品の技術傾向ライン項目を使わなければならない。

述べたように、DRAM の千鳥コンタクトあり M1 ハーフピッチの値は最も挑戦的な配線ハーフピッチを表しており、先端リソのライン・スペース解像度をドライブしているので、DRAM M1 ハーフピッチは 2005 年版 ITRS の共通表の参照ヘッダーとして使われている。他の個々の製品の技術傾向は引き続き DRAM M1 ハーフピッチに対し監視し、将来は総合的なリソの解像度が他の製品のパターン寸法傾向でドライブされるかもしれない。

例えば、下に詳しく付加して述べたように、Flash メモリのコンタクト無しポリ・ハーフピッチは近い将来 DRAM の千鳥コンタクト有り M1 ハーフピッチより 1 年先に進むと予想されている。Flash メモリのコンタクト無しポリ・ハーフピッチによる 1 年の先行は、DRAM の千鳥コンタクト有り M1 ハーフピッチと(リソ・プロセスの難しさから)等価であると考えられている。しかし、更に先行が進めば、Flash メモリ技術が先進リソをドライブするかもしれない。「生産の年」のタイミング定義に関する用語集部分の詳細を参照されたい。

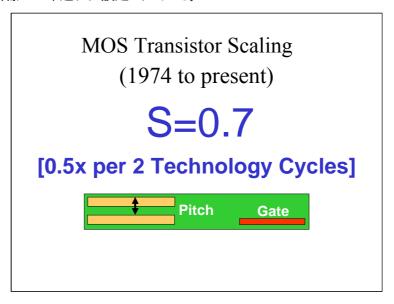

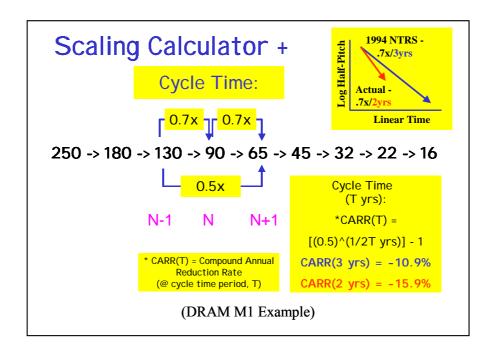

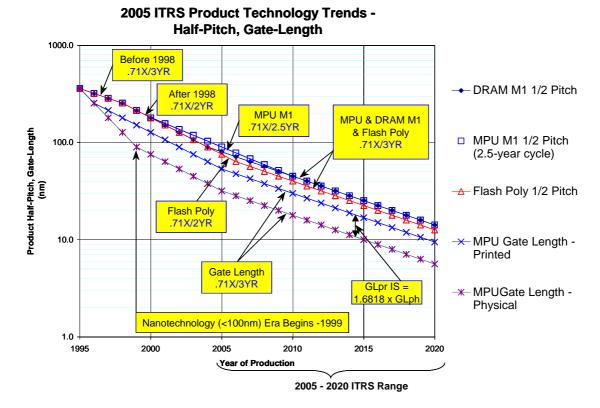

2005年版 ITRS 表の技術傾向目標は今や 2005年から 15年間の 2020年までの ITRS ロードマップ限界で完全に年毎に記述されている。しかしながら、前に確立した IRC のガイドラインに従って、2005年版 ITRS は、技術傾向サイクルタイムをプロセス技術において重要な進歩が達成される期間とする定義も残してある。明確には、技術傾向サイクルタイムの進歩は 1 サイクルで約 0.71 倍の縮小(2 サイクルで正確に 0.50 倍)を達成する期間として引き続き定義されている。Figure6、7を参照のこと。

2005 年版 ITRS の ORTCTable1a, 1b で技術サイクル・タイミングが製品で異なっていることに注意して欲しい。 例えば、DRAM の千鳥コンタクト有り M1 ハーフピッチは(実際の 2000 年 180nm からの 2 年サイクルに基づいていた後)3 年で 0.71 倍(6 年で 0.5 倍)のタイミング・サイクルに基づいて予想されており、これは歴史的な事実の 2004 年 90nm から 2019 年 16nm 目標に至っている。3 年サイクル・タイミングの毎年の縮小率は年 0.8909 倍でこれは、中間の年毎の傾向目標(例えば、2005 年 80nm、2020 年 14nm)を計算する時に用いられている。

入手できる産業界のデータ、ITWG や IRC のインプットを考慮に入れた後、コンタクトなしポリシリコン・ハーフピッチの定義に基づき、新しい Flash 製品技術タイミング・モデルに関してコンセンサスが得られた。Flash メモリのコンタクト無しポリ・ハーフピッチは 2000 年 180nm から 2006 年 64nm まで、2 年サイクル・タイミング速さである。この点に関しリソの ITWG により、Flash メモリのコンタクト無しポリ・ハーフピッチは数値的には DRAM の千鳥コンタクト有り M1 ハーフピッチより、同じプロセス技術や装置が目標を達成するために用いられたとして、1 年前倒しできることが確認された。しかしながら、2006 年 64nm 以降 Flash メモリのコンタクト無しポリ・ハーフピッチは 3 年タイミング・サイクルになり、正確に DRAM の傾向に 1 年先行し、2020 年 13nm まで年毎に続くであろう。

上に述べたように MPU(と高性能 ASIC)の製品傾向サイクル・タイミングは 2005 年版 ITRS で変化し、DRAM と同じ千鳥コンタクト有り M1 ハーフピッチに基づくようになった。 歴史的データの分析と ITWG と IRC のコンセンサスにより、 MPU M1 ハーフピッチは歴史的な 2000 年 180nm の実データの点から 2010 年 45nm まで 2.5 年サ

イクル・タイミング(5年で0.5倍)になった。2010年45nmの点で、MPU M1目標はDRAM M1 サイクル・タイミング目標に追いつき、同じになって(3年タイミング・サイクルで)2020年のロードマップの終わりまで続くであろう。

MPU(と高性能 ASIC)の最終的な物理ゲート長(phGL)目標は 2003 年版 ITRS と変わっていない。2003 年版 ITRS ではタイミングは 2 年サイクル(4 年で 0.5 倍、年 0.8909 倍)で 1999 年から 2005 年で 32nm となり、それから傾向は 3 年タイミング・サイクル(6 年で 0.5 倍、年 0.8909 倍)でロードマップの最後 2020 年で 6nm になる。 リソと FEP の ITWG はエッチ後の最終的な物理ゲート長と露光ゲート長目標間の比に関して新しい合意(1.6818 × 上記物理ゲート長縮小率)に達した。

低消費電力 LOP ASIC のゲート長目標は、PIDsの ITWG で確立され、MPU(と高性能 ASIC)の露光ゲート 長と物理的ゲート長目標の2年遅れに設定されている。

Figure 6 MOS Transistor Scaling—1974 to present

Figure 7 Scaling Calculator

(注) NTRS (National Technology Roadmap for Semiconductors: 米国内半導体技術ロードマップ)

# ロードマップのタイムライン

2005 年版ロードマップは、2005 年を基準年として 2020 年までの 15 年間の予測を表している。DRAM 製品の将来の技術革新の速さのタイミング傾向が、千鳥コンタクト有り M1 ハーフピッチに対する先端性を依然として代表しており、2004 年 90nm 後 3 年サイクル(3 年毎にパターン寸法の 0.71 倍)に戻ることが予想されていることは 2003 年版と変わっていない。PIDS TWG による最新の調査によると、90nm DRAM ハーフピッチ製品は 2004 年に、2003 年版 ITRS で DRAM 製品の「製造」定義の明確な必要項目となった顧客による製品信頼性認定に基づき製造立ち上げが始まっている。

2001 年版ITRSでは、130nm DRAM 製品 M1 ハーフピッチは 1 年前倒しされ(1999 年版 ITRS の 2002 年から 2001 年へ)、350nm/1995 年以来の歴史的傾向である 2 年技術サイクルを継続している(1997 年 250nm、1999 年 180nm)ように思われた。2003 年の DRAM 製造業者からの、厳しい顧客製品認定に基づく量産立ち上げデータによれば実際の量産立ち上げ時期は次のようであった:350nm/1995、250nm/1998、180nm/2000、130nm/2002、この新しいデータは 2 年のサイクル・タイミングを示しているが、元の 2001 年版ITRSより 1 年遅れている。PIDs メンバーが確認した所によると、2004 年に量産立ち上げが行なわれた実際の DRAM のデータから 2002 年 130nm、2004 年 90nm の 2 年サイクルが存在した。この新しい遅れた 2 年サイクルの傾向が続く可能性もあったが、今日の DRAM 製品の製造者のコンセンサスは、PIDs の最新調査が確認したように、DRAM 千鳥コンタクト 有り M1 ハーフピッチに関し、2005 から 2020 年のロードマップ期間に関し Figure8 に示すように、3 年タイミングサイクル(0.71 倍削減)を予定している。

上に述べたように、技術サイクル(0.71 倍のパターン寸法の削減)の達成を定義する上で、DRAM 配線ハーフピッチが、半導体製造の先端技術を最も良く表す機能として使用され続けるだろう。しかし、Flash コンタクト無しポリシリコン・ハーフピッチ・パターンが DRAM MI を陵駕し、今や先端製造技術のドライバーともなっている。同様に、遅れていた MPU や ASIC MI 千鳥コンタクト有り配線ハーフピッチは 2.5 年のより早いサイクル・ペースで進歩しており、現在のところ 2010 年 45nmで DRAM ハーフピッチに追いつき同じペースとなることが期待されている。2005 年版 ITRS の新製品を指向して焦点を当てることで、全ての製品技術傾向が監視される。その製品傾向の何れかが、更に加速を起こし、先端技術において、産業の研究や装置・材料サプライヤをドライブするかもしれない。Figure8 参照。

#### 丸められたトレンド数値

新しい DRAM ハーフピッチ・データの入力の結果と 180nm を傾向の計算起点としているため、2005 年版 ITRS には、技術サイクル傾向目標について、過去の「四捨五入」方式の訂正が含まれている。 実際の数学的な 傾向では、2 技術サイクル毎に 50%縮小とし、四捨五入で丸められたノード数値は、1995 年の 350nm から始まり、以下の TableC のようになっている。

| YEAR OF<br>PRODUCTION            | 1995 | 1998 | 2000 | 2002  | 2003 | 2004 | 2006 | 2007 | 2009 | 2010 | 2012 | 2013 | 2015 | 2016 | 2018 | 2019 |

|----------------------------------|------|------|------|-------|------|------|------|------|------|------|------|------|------|------|------|------|

| Calculated Trend<br>Numbers (nm) | 360  | 255  | 180  | 127.3 | 101  | 90   | 71.4 | 63.6 | 50.5 | 45   | 35.7 | 31.8 | 25.3 | 22.5 | 17.9 | 15.9 |

| ITRS Rounded<br>Numbers (nm)     | 350  | 250  | 180  | 130   | 100  | 90   | 70   | 65   | 50   | 45   | 36   | 32   | 25   | 22   | 18   | 16   |

Table C Rounded versus Actual Trend Numbers (DRAM Product Trend Example)

半導体産業が新ナノ技術(サブ 100nm)の二桁技術ノードに入ると、新しい「四捨五入」の訂正が非常に重要になることに注意して頂きたい。いくつかの分野では、過去の ITRS との整合性をとって、100nm/2003 から始まる以前の技術世代を引き続き採用する権利を持っている。これにより、現行の 2003 年版ロードマップの慣行 (70nm/2006; 50nm/2009; 35nm/2012; 25nm/2015)よりも 1 年早い時点にマイルストーンが置かれることになる。IRC

の合意事項として、長期の計算には両方の数値の組み合わせが入手できる。もとの 2001 年版 ITRS の長期の欄(2010/hp45/45nm; 2013/hp32/32nm; 2016/hp22/22nm)が残され、新しい欄(2012/35nm; 2015/25nm; 2018/18nm)が加えられている。

#### **ORTCへの改定**

MPU/ASIC M1 ハーフピッチを DRAM と同じ千鳥コンタクト有りハーフピッチと再定義することに加えて、2005 年版 ITRS ORTC 技術目標ライン項目として、Flash 製品のコンタクトなしポリシリコン・ハーフピッチが新たに追加された。これは、ORTC の Table1a と 1b に加えられており、以前の MPU コンタクト無しハーフピッチ項は削除されている。

描画された MPU ゲート長については、2001 年版 ITRS の積極的とも言える開始点に大きな訂正が行われた。 更に、プロセス処理したトランジスタのボトム・ゲート長寸法をさらに縮小する新物理ゲート長は、現在調査確認が行われている。 物理ゲート長の傾向は 2003 年と 2005 年版 ITRS では変更無く、2020 年のロードマップの限界まで DRAM ハーフピッチの傾向予測と一致して、3 年サイクルで約 70%のスケーリングが続くと予測される。 Figure8 参照。

業界のリーダシップを獲得するため、スケジュールを前倒しで達成しなければならない目標のセットとして、ORTC の技術数値は、半導体関連企業により頻繁に使用されている。このように、激しい競争的環境に置かれている半導体産業では、ORTC の技術数値の大半が、すなわちロードマップそのものが時代遅れになる恐れがある。我々が行う毎年の改訂作業では、技術の方向性に関する充分に密着した追跡を国際コンセンサスの場で行うことで、半導体産業における ITRS の有用性を維持することを期待している。

たとえば、会社の調査データや公の発表と伴に実際のデータや学会の論文を、個々の製品の技術傾向の中で2年ノード・サイクル継続の可能性とともに、2006年ITRSの改訂作業で再評価する。特に、ロジックと Flash 製品のハーフピッチの加速を、将来技術の主導権をとる候補として監視する。

上に述べたように、様々なサイクルを反映し、将来のロードマップのシフトを密着して監視するため、2005 年 ~ 2013 年までの「短期」と呼ばれる期間の毎年の技術要求を発表し、2014 年から 2020 年までの「長期」と呼ばれる期間の毎年の技術要求を発表することが同意されている。

Figure 8 2005 ITRS—Half Pitch and Gate Length Trends

### 製品世代およびチップ寸法モデル

このセクションでは、「製品世代」およびその技術サイクルとの関係を述べる。というのは、今までこの 2 つの用語を頻繁に区別なく使用してきたからである。しかしながら、3 年ごとに新しい DRAM 製品世代(前世代密度の4 倍で、基本的に新しい技術機能群に基づく)が誕生するという今までの単純な図式は、技術サイクル・タイミングの進歩を定義する手段として時代遅れになっている。この 2005 年版 ITRS では、単一の「技術ノード」、「hpXX」への言及は削除されている。これは、先端製品の進化/縮小のパスが複雑になるにつれ、市場の機能・性能・値ごろ感の要求に基づいて、個々の製品技術傾向がお互いに異なった速さで進展することを反映したものである。

歴史的にいえば、DRAM 製品は全半導体産業の技術の動輪として認識されてきた。1990 年代後期より前にさかのぼると、ロジック(MPU で代表される)技術は DRAM 技術と同じ速さで進展していた。しかし、2000 年180nm ロジック製品がゆっくりした 2.5 年の速さで進展し始め、他方 DRAM 技術は加速された 2 年速さで引き続き進展した。ここ数年の間に、マイクロプロセッサ製造に使用される新規技術の開発速度は 2.5 年速さを続け、他方 DRAM は減速して 2020 年のロードマップの限界まで 3 年サイクル速さとなることが予測されている。より速い 2.5 年サイクル速さを継続する結果、マイクロプロセッサ製品は DRAM とのハーフピッチ技術格差を縮めることになり、現在では特に、露光ゲート長と物理ゲート長の孤立ライン・パターンを処理する能力について、最先端のリソグラフィ装置およびプロセスの開発を推し進めている。加えるに、Flash 技術はコンタクト無しポリシリコンで定義されているので、最先端技術で開発を進めてられている点まで加速をしている。2005 年版ロードマップでは、DRAM 製品が依然として開発をリードしているが、Flash とマイクロプロセッサー製品も今や技術リーダシップの役割を共有している。

しかしながら、この 2 つの製品ファミリの間には、いくつかの基本的な差異が存在する。コスト削減および工場 生産性向上への商品市場の経済的な圧力が強いために、DRAM 製品ではチップ寸法の最小化が強調されて いる。 そのため DRAM の技術開発は、主にメモリ・セル占有面積の最小化に焦点が当てられている。 しかしなが ら、このセル寸法最小化の圧力は、セル容量最大化の要求と矛盾してしまう。このセル容量最大化要求は、メモリ・セル設計者にプレッシャーをかけ、セル寸法を縮小しながら容量の最低必要条件を満たすように設計と材料にわたって創造的な手段を探求させている。その上、最小面積に最大数の DRAM セルを密に実装するためには、セル・ピッチの最小化が必要となる。

マイクロプロセッサでも、最高性能を保ちつつコスト削減を達成するという市場圧力が強くかかっている。主にトランジスタ・ゲート長と配線層数により、高性能が可能なものとなる。ORTC 表に関する所要の機能、チップ寸法、セル面積、密度などについて、2005 年版 ITRS チームは意見の一致をみている。MPU 製品チップ寸法表は、導入時の大きなチップ寸法が時を経て手ごろなチップ寸法を達成しなければならないので、より DRAM モデルと同一なように見える。追加のライン項目が加えられ、モデルのコンセンサスを伝え、背景にあるモデルの仮定がORTC 表の注に含まれている。短期と長期の技術傾向指標の要約を Table1a と Table1b に示す。同意されたように DRAM MI ハーフピッチに関連した ITRS 技術「ノード」を示す hp X X は削除したが、DRAM は継続してDRAM ハーフピッチであり、また積極的に MPU ゲート長を縮小し性能を促進する素子寸法も含まれている。表の完全性を図るため、MPU/ASIC 製品-メタル・ハーフピッチも検討して載せており、そのペースは、わずかにDRAM ハーフピッチに遅れるが 2010 年以降は等しくなるだろう。ASIC/低電力のゲート長も含まれてはいるが、待機電流および動作電流を最大にするために最先端 MPU よりは遅れている。ハーフピッチとゲート長の特長に関する詳細な定義については、用語解説セクションを参照して頂きたい。各製品世代について、最先端の(「現在導入中」)DRAM 製品と量産(「現在量産中」)DRAM 製品の双方を示す。

要約すると、DRAM コンタクト有り M1 ハーフピッチ・パターン寸法の長期平均年縮小率は 2004 年 90nm 以降 3 年の技術サイクル速さに戻ることを予測していることに注目して欲しい。これは、年約 11%(3 年約 30%縮小)を表している。以前(1998 年 250nm から 2004 年 90nm)の加速された 2 年サイクルは年間平均縮小率が約 16%/年(2 年約 30%縮小)である。上述のとおり、新 Flash メモリコンタクト無しポリシリコンは DRAM M1 を追い越し、2006 年に 3 年速さになり、MPU/ASIC M1 (グラフでは MPU と元々記述)は 2010 年 45nm で DRAM M1 に追いつき、3 年速さに戻る(Figure8 参照)。

| Year of Production                                      | 2005 | 2006 | 2007 | 2008 | 2009 | 2010 | 2011 | 2012 | 2013 |

|---------------------------------------------------------|------|------|------|------|------|------|------|------|------|

| DRAM ½ Pitch (nm) (contacted)                           | 80   | 70   | 65   | 57   | 50   | 45   | 40   | 36   | 32   |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm)                      | 90   | 78   | 68   | 59   | 52   | 45   | 40   | 36   | 32   |

| MPU Printed Gate Length (nm) ††                         | 54   | 48   | 42   | 38   | 34   | 30   | 27   | 24   | 21   |

| MPU Physical Gate Length (nm)                           | 32   | 28   | 25   | 23   | 20   | 18   | 16   | 14   | 13   |

| ASIC/Low Operating Power Printed Gate<br>Length (nm) †† | 76   | 64   | 54   | 48   | 42   | 38   | 34   | 30   | 27   |

| ASIC/Low Operating Power Physical Gate<br>Length (nm)   | 45   | 38   | 32   | 28   | 25   | 23   | 20   | 18   | 16   |

| Flash ½ Pitch (nm) (un-contacted Poly)(f)               | 76   | 64   | 57   | 51   | 45   | 40   | 36   | 32   | 28   |

Table 1a Product Generations and Chip Size Model Technology Trend Targets—Near-term Years

Table 1b Product Generations and Chip Size Model Technology Trend Targets—Long-term Years

| Year of Production                                   | 2014 | 2015 | 2016 | 2017 | 2018 | 2019 | 2020 |

|------------------------------------------------------|------|------|------|------|------|------|------|

| DRAM ½ Pitch (nm) (contacted)                        | 28   | 25   | 22   | 20   | 18   | 16   | 14   |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm)                   | 28   | 25   | 22   | 20   | 18   | 16   | 14   |

| MPU Printed Gate Length (nm) ††                      | 19   | 17   | 15   | 13   | 12   | 11   | 9    |

| MPU Physical Gate Length (nm)                        | 11   | 10   | 9    | 8    | 7    | 6    | 6    |

| ASIC/Low Operating Power Printed Gate Length (nm) †† | 24   | 21   | 19   | 17   | 15   | 13   | 12   |

| ASIC/Low Operating Power Physical Gate Length (nm)   | 14   | 13   | 11   | 10   | 9    | 8    | 7    |

| Flash ½ Pitch (nm) (un-contacted Poly)(f)            | 25   | 23   | 20   | 18   | 16   | 14   | 13   |

#### Notes for Tables 1a and 1b:

†† MPU and ASIC gate-length (in resist) node targets refer to the most aggressive requirements, as printed in photoresist (which was by definition also "as etched in polysilicon," in the 1999 ITRS).

However, during the 2000/2001 ITRS development, trends were identified, in which the MPU and ASIC "physical" gate lengths may be reduced from the "as-printed" dimension. These physical gate-length targets are driven by the need for maximum speed performance in logic microprocessor (MPU) products, and are included in the Front End Processes (FEP), Process Integration, Devices, and Structures (PIDs), and Design chapter tables as needs that drive device design and process technology requirements.

Refer to the Glossary for definitions of Introduction, Production, InTERgeneration, and InTRAgeneration terms.

MPU Physical Gate Length targets are unchanged from the 2003 ITRS and 2004 ITRS Update, but also included are the complete set of annualized Long-term targets through 2020. The printed gate length has been adjusted to reflect the agreement between the FEP and Lithography TWGs to use a standard factor, 1.6818, to model the relationship between the final physical gate length and the printed gate length, after additional processing is applied to that isolated feature.

MPU/ASIC M1 stagger-contact targets have been accelerated to 90 nm in 2005 to reflect actual industry performance per the Interconnect ITWG recommendation, and a new consensus model technology cycle timing of 2.5 years (to  $0.71 \times$  reduction) has been applied through 2010, when the trend targets become equal to the DRAM stagger-contact M1 through 2020.

Numbers in the header are rounded from the actual trend numbers used for calculation of models in ITRS ORTC and ITWG tables (see discussion in the Executive Summary on rounding practices).

Table 1c DRAM and Flash Production Product Generations and Chip Size Model—Near-term Years

| Year of Production                               | 2005   | 2006    | 2007    | 2008    | 2009    | 2010    | 2011    | 2012    | 2013    |

|--------------------------------------------------|--------|---------|---------|---------|---------|---------|---------|---------|---------|

| DRAM ½ Pitch (nm) (contacted)                    | 80     | 70      | 65      | 57      | 50      | 45      | 40      | 36      | 32      |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm)               | 90     | 78      | 68      | 59      | 52      | 45      | 40      | 36      | 32      |

| MPU Physical Gate Length (nm)                    | 32     | 28      | 25      | 23      | 20      | 18      | 16      | 14      | 13      |

| DRAM Product Table                               |        |         |         |         |         |         |         |         |         |

| Cell area factor [a]                             | 8      | 8       | 8       | 6       | 6       | 6       | 6       | 6       | 6       |

| Cell area [Ca = af2] (mm²)                       | 0.051  | 0.041   | 0.032   | 0.019   | 0.015   | 0.012   | 0.0096  | 0.0077  | 0.0061  |

| Cell array area at production (% of chip size) § | 63.00% | 63.00%  | 63.00%  | 56.08%  | 56.08%  | 56.08%  | 56.08%  | 56.08%  | 56.08%  |

| Generation at production §                       | 1G     | 2G      | 2G      | 2G      | 4G      | 4G      | 4G      | 8G      | 8G      |

| Functions per chip (Gbits)                       | 1.07   | 2.15    | 2.15    | 2.15    | 4.29    | 4.29    | 4.29    | 8.59    | 8.59    |

| Chip size at production (mm²)§                   | 88     | 139     | 110     | 74      | 117     | 93      | 74      | 117     | 93      |

| Gbits/cm2 at production §                        | 1.22   | 1.54    | 1.94    | 2.91    | 3.66    | 4.62    | 5.82    | 7.33    | 9.23    |

| Flash Product Table                              |        |         |         |         |         |         |         |         |         |

| Flash ½ Pitch (nm) (un-contacted Poly)(f)        | 75.7   | 63.6    | 56.7    | 50.5    | 45.0    | 40.1    | 35.7    | 31.8    | 28.3    |

| Cell area factor [a]                             | 4.0    | 4.0     | 4.0     | 4.0     | 4.0     | 4.0     | 4.0     | 4.0     | 4.0     |

| Cell area [Ca = af²] (mm²)                       | 0.023  | 0.016   | 0.013   | 0.010   | 800.0   | 0.006   | 0.005   | 0.004   | 0.003   |

| Cell array area at production (% of chip size) § | 67.5%  | 67.5%   | 67.5%   | 67.5%   | 67.5%   | 67.5%   | 67.5%   | 67.5%   | 67.5%   |

| Generation at production § SLC                   | 4G     | 4G      | 4G      | 8G      | 8G      | 8G      | 16G     | 16G     | 16G     |

| Generation at production § MLC                   | 8G     | 8G      | 8G      | 16G     | 16G     | 16G     | 32G     | 32G     | 32G     |

| Functions per chip (Gbits) SLC                   | 4.29   | 4.29    | 4.29    | 8.59    | 8.59    | 8.59    | 17.18   | 17.18   | 17.18   |

| Functions per chip (Gbits) MLC                   | 8.59   | 8.59    | 8.59    | 17.18   | 17.18   | 17.18   | 34.36   | 34.36   | 34.36   |

| Chip size at production (mm²)§ SLC               | 144    | 101.8   | 80.8    | 128.3   | 101.8   | 80.8    | 128.3   | 101.8   | 80.8    |

| Chip size at production (mm²)§ MLC               | 144    | 101.8   | 80.8    | 128.3   | 101.8   | 80.8    | 128.3   | 101.8   | 80.8    |

| Gbits/cm² at production § SLC                    | 3E+09  | 4.2E+09 | 5.3E+09 | 6.7E+09 | 8.4E+09 | 1.1E+10 | 1.3E+10 | 1.7E+10 | 2.1E+10 |

| Gbits/cm² at production § MLC                    | 6E+09  | 8.4E+09 | 1.1E+10 | 1.3E+10 | 1.7E+10 | 2.1E+10 | 2.7E+10 | 3.4E+10 | 4.3E+10 |

Year of Production 2014 2015 2016 2017 2018 2019 2020 DRAM ½ Pitch (nm) (contacted) 28 25 22 20 18 16 14 MPU/ASIC Metal 1 (M1) ½ Pitch (nm) 28 25 22 20 18 16 14 MPU Physical Gate Length (nm) 7 11 10 9 8 6 6 DRAM Product Table Cell area factor [a] 6 6 6 6 6 6 6 0.0048 0.0038 0.0030 0.0024 0.0019 0.0015 0.0012 Cell area [Ca =  $af^2$ ] ( $mm^2$ ) Cell array area at production (% of chip size) § 56.08% 56.08% 56.08% 56.08% 56.08% 56.08% 56.08% Generation at production § 8G 16G 16G 16G 32G 32G 32G 8.59 17.18 17.18 17.18 34.36 34.36 34.36 Functions per chip (Gbits) 74 117 93 74 117 93 74 Chip size at production (mm²)§ Gbits/cm2 at production § 11.63 14.65 18.46 23.26 29.31 36.93 46.52 Flash Product Table Flash ½ Pitch (nm) (un-contacted Poly)(f) 25.3 22.5 20.0 17.9 15.9 14.2 12.6 4.0 4.0 4.0 4.0 4.0 4.0 Cell area factor [a] 4.0 Cell area [Ca =  $af^2$ ] (mm<sup>2</sup>) 0.003 0.002 0.002 0.001 0.001 0.001 0.001 Cell array area at production (% of chip size) § 67.5% 67.5% 67.5% 67.5% 67.5% 67.5% 67.5% Generation at production § SLC 32G 32G 64G 64G 64G 128G 32G Generation at production § MLC 64G 128G 128G 256G 64G 64G 128G Functions per chip (Gbits) SLC 34.36 34.36 34.36 68.72 68.72 68.72 137.44 Functions per chip (Gbits) MLC 68.72 68.72 68.72 137.44 137.44 137.44 274.88 Chip size at production (mm²)§ SLC 128.3 101.8 80.8 128.3 101.8 80.8 128.3 128.3 128.3 128.3 101.8 80.8 101.8 80.8 Chip size at production (mm²)§ MLC 2.7E+10 3.4E+10 4.3E+10 5.4E+10 6.7E+10 8.5E+10 1.1E+11 Gbits/cm<sup>2</sup> at production § SLC 1.3E+11 5.4E+10 6.7E+10 8.5E+10 1.1E+11 1.7E+11 2.1E+11 Gbits/cm<sup>2</sup> at production § MLC

Table 1d DRAM and Flash Production Product Generations and Chip Size Model—Long-term Years

Notes for Tables 1c and 1d:

§ DRAM Model—cell area factor (design/process improvement) targets are as follows:

1999–2007/8×: 2008-2020/6×. Due to the elimination of the "7.5," "7," and the "5" DRAM Cell design improvement Factors [a] in the latest 2005 ITRS DRAM consensus model, the addition of "Moore's Law" bits/chip slows from 2× every 2.5–3 years to 2× every three years.

DRAM product generations were increased by 4×bits/chip every four years with interim 2×bits/chip generation. However, in the latest model 2005 ITRS timeframe refer to Figures 9 and 10 for bit size and bits/chip trends:

- 1. at the Introduction phase, after the 16 Gbit generation, the introduction rate is  $4 \times \sin y$  ears ( $2 \times \tan y$ ); and

- 2. at the Production phase, after the 4 Gbit generation, the introduction rate is  $4 \times \sin y$  years ( $2 \times \tan y$ ).

As a result of the DRAM consensus model changes for the 2005 ITRS, the InTER-generation chip size growth rate model target for Production-phase DRAM products remains "flat" at less than  $140 \text{ mm}^2$ , similar to the MPU model. However, with the elimination of some of some of "cell area factor" reductions, the flat-chip-size model target requires the bits/chip "Moore's Law" model for DRAM products to increase the time for doubling bits per chip to an average of  $2 \times \text{per } 3$  years (see ORTC Table 1c, 1d).

Furthermore, the cell array efficiency (CAE – the Array % of total chip area) was corrected to 56.1% after 2008, since only the storage cell array area benefits from the  $6\times$  "cell area factor" improvement, not the periphery. This CAE change in the model puts even additional pressure on the production-phase product chip size to meet the target flat-chip-size model. It can be observed in the Table 1c and d model data that the InTRA-generation chip size shrink model is still  $0.5\times$  every technology cycle (to  $0.71\times$  reduction) inbetween cell area factor reductions.

Refer to the Glossary for definitions of Introduction, Production, InTERgeneration, and InTRAgeneration terms.

Similarly to DRAM, the new Flash product model also targets an affordable (<145 mm²) chip size and includes a doubling of functions (bits) per chip every technology cycle (three years after 2006) on an Inter-generation. Flash cells have reached a limit of the 4-design factor, so the reduction of the Flash single-level cell (SLC) size is paced by the uncontacted polysilicon (three-year cycle). However, the Flash technology has the ability to store and electrically access two bits in the same cell area, creating a multi-level-cell (MLC) "virtual" per-bit size that is one-half the size of an SLC product cell size (refer to Figures 9 and 10).

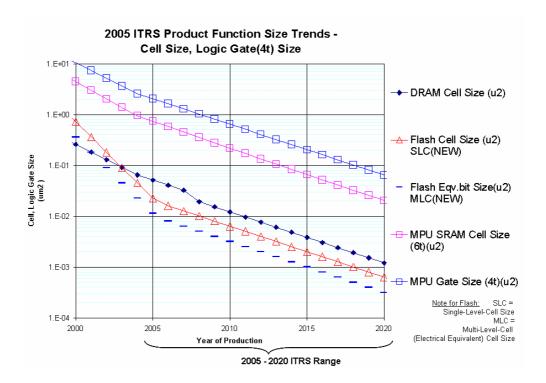

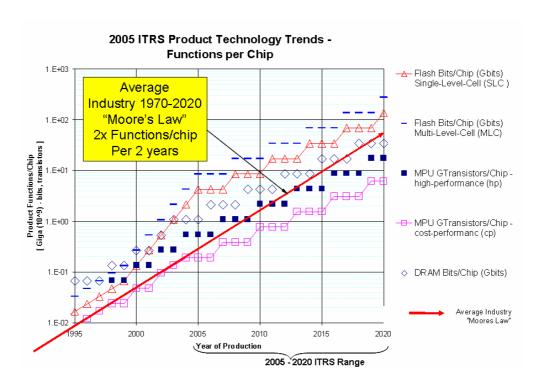

Figure 9 2005 ITRS Product Function Size Trends:

MPU Logic Gate Size (4-transistor); Memory Cell Size [SRAM (6-transistor); Flash (SLC and MLC), and DRAM

(transistor + capacitor)]

Figure 10 2005 ITRS Product Technology Trends: Product Functions/Chip and Industry Average "Moore's Law" Trends

Year of Production 2005 2006 2007 2008 2009 2010 2011 2012 2013 DRAM 1/2 Pitch (nm) (contacted) *80* 70 65 57 50 45 40 36 32 MPU/ASIC Metal 1 (M1) 1/2 Pitch (nm) (f) 90 78 68 59 52 45 40 36 32 MPU Physical Gate Length (nm) 32 28 25 23 20 18 16 14 13 Cell area factor [a] 6 8 8 8 6 6 6 6 6 0.051 0.041 0.032 0.019 0.015 0.012 0.010 800.0 0.006 Cell area [Ca =  $af^2$ ] (mm<sup>2</sup>) 74.30% 72.95% 73.25% 73.52% 73.76% 73.97% 74.16% 74.47% 74.61% Cell array area at introduction (% of chip size) § Generation at introduction § 8G 16**G** 16G 16**G** 32G 32G 32G 64G Functions per chip (Gbits) 8.59 8.59 17.18 17.18 17.18 34.36 34.36 34.36 68.72 606 479 757 449 356 563 446 353 560 Chip size at introduction (mm²) § 1.42 1.79 2.27 3.82 4.83 6.10 7.70 9.73 12.28 Gbits/cm² at introduction §

Table 1e DRAM Introduction Product Generations and Chip Size Model—Near-term Years

Table 1f DRAM Introduction Product Generations and Chip Size Model—Long-term Years

| Year of Production                                 | 2014   | 2015   | 2016   | 2017   | 2018   | 2019   | 2020   |

|----------------------------------------------------|--------|--------|--------|--------|--------|--------|--------|

| DRAM ½ Pitch (nm) (contacted)                      | 28     | 25     | 22     | 20     | 18     | 16     | 14     |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm) (f)             | 28     | 25     | 22     | 20     | 18     | 16     | 14     |

| MPU Physical Gate Length (nm)                      | 11     | 10     | 9      | 8      | 7      | 6      | 6      |

| Cell area factor [a]                               | 6      | 6      | 6      | 6      | 6      | 6      | 6      |

| Cell area [Ca = $af^2$ ] (mm <sup>2</sup> )        | 0.005  | 0.004  | 0.003  | 0.002  | 0.002  | 0.002  | 0.001  |

| Cell array area at introduction (% of chip size) § | 74.70% | 74.83% | 74.93% | 75.00% | 75.09% | 75.18% | 75.27% |

| Generation at introduction §                       | 64G    | 64G    | 128G   | 128G   | 128G   | 256G   | 256G   |

| Functions per chip (Gbits)                         | 68.72  | 68.72  | 137.44 | 137.44 | 137.44 | 274.88 | 274.88 |

| Chip size at introduction (mm²) §                  | 444    | 351    | 557    | 442    | 350    | 555    | 440    |

| Gbits/cm² at introduction §                        | 15.49  | 19.55  | 24.67  | 31.11  | 39.24  | 49.50  | 62.44  |

Notes for Tables 1e and 1f:

§ DRAM Model—cell area factor (design/process improvement) targets are as follows:

1999–2007/8×: 2008-2020/6×. Due to the elimination of the "7.5," "7," and the "5" DRAM Cell design improvement Factors [a] in the latest 2005 ITRS DRAM consensus model, the addition of "Moore's Law" bits/chip slows from 2× every 2.5–3 years to 2× every three years.

DRAM product generations were increased by 4×bits/chip every four years with interim 2×bits/chip generation. However, in the latest model 2005 ITRS timeframe:

1. at the Introduction phase, after the 16 Gbit generation, the introduction rate is  $4 \times six$  years ( $2 \times three$  years); and

2. at the Production phase, after the 4 Gbit generation, the introduction rate is 4×six years (2×three years).

As a result of the DRAM consensus model changes for the 2005 ITRS, the InTER-generation chip size growth rate model target for production-phase DRAM products remains "flat" at less than 140 mm<sup>2</sup>, similar to the MPU model. However, with the elimination of some of some of "cell area factor" reductions, the flat-chip-size model target requires the bits/chip "Moore's Law" model for DRAM products to increase the time for doubling bits per chip to an average of  $2 \times$  per three years (see ORTC Table 1c, d).

Furthermore, the cell array efficiency (CAE – the Array % of total chip area) was corrected to 56.1% after 2008, since only the storage cell array area benefits from the 6× "cell area factor" improvement, not the periphery. This CAE change in the model puts even additional pressure on the Production-phase product chip size to meet the target flat-chip-size model. It can be observed in the Table 1c and d model data that the InTRA-generation chip size shrink model is still  $0.5 \times \text{every}$  technology cycle (to  $0.71 \times \text{reduction}$ ) inbetween cell area factor reductions.

Refer to the Glossary for definitions of Introduction, Production, InTERgeneration, and InTRAgeneration terms.

Table 1g MPU (High-volume Microprocessor) Cost-Performance Product Generations and Chip Size Model—Near-term Years

|                                                                                    | •     |       |       |       |       |       |       |       |       |

|------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| Year of Production                                                                 | 2005  | 2006  | 2007  | 2008  | 2009  | 2010  | 2011  | 2012  | 2013  |

| DRAM ½ Pitch (nm) (contacted)                                                      | 80    | 70    | 65    | 57    | 51    | 45    | 40    | 36    | 32    |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm) (f)                                             | 90    | 78    | 68    | 59    | 52    | 45    | 40    | 36    | 32    |

| MPU Physical Gate Length (nm)                                                      | 32    | 28    | 25    | 23    | 20    | 18    | 16    | 14    | 13    |

| SRAM Cell (6-transistor) Area factor ++                                            | 115.6 | 113.7 | 111.9 | 110.4 | 109.0 | 107.8 | 106.7 | 105.7 | 104.8 |

| SRAM Cell (6-transistor) Area factor ++                                            | 91.8  | 94.5  | 97.5  | 100.7 | 104.1 | 107.8 | 106.7 | 105.7 | 104.8 |

| Logic Gate (4-transistor) Area factor ++                                           | 320   | 320   | 320   | 320   | 320   | 320   | 320   | 320   | 320   |

| Logic Gate (4-transistor) Area factor ++                                           | 254   | 266   | 279   | 292   | 306   | 320   | 320   | 320   | 320   |

| SRAM Cell (6-transistor) Area efficiency ++                                        | 0.63  | 0.63  | 0.63  | 0.63  | 0.63  | 0.63  | 0.63  | 0.63  | 0.63  |

| Logic Gate (4-transistor) Area efficiency ++                                       | 0.50  | 0.50  | 0.50  | 0.50  | 0.50  | 0.50  | 0.50  | 0.50  | 0.50  |

| SRAM Cell (6-transistor) Area ++                                                   | 0.74  | 0.58  | 0.45  | 0.35  | 0.28  | 0.22  | 0.17  | 0.13  | 0.11  |

| SRAM Cell (6-transistor) Area w/overhead ++                                        | 1.2   | 0.93  | 0.73  | 0.57  | 0.45  | 0.35  | 0.27  | 0.22  | 0.17  |

| Logic Gate (4-transistor) Area ++                                                  | 2.06  | 1.63  | 1.30  | 1.03  | 0.82  | 0.65  | 0.51  | 0.41  | 0.32  |

| Logic Gate (4-transistor) Area w/overhead ++                                       | 4.1   | 3.3   | 2.6   | 2.1   | 1.6   | 1.3   | 1.03  | 0.82  | 0.65  |

| Transistor density SRAM (Mtransistors/cm²)                                         | 504   | 646   | 827   | 1,057 | 1,348 | 1,718 | 2,187 | 2,781 | 3,532 |

| Transistor density logic (Mtransistors/cm²)                                        | 97    | 122   | 154   | 194   | 245   | 309   | 389   | 490   | 617   |

| Generation at introduction *                                                       | р07с  | p10c  | p10c  | p10c  | p13c  | p13c  | p13c  | p16c  | p16c  |

| Functions per chip at introduction (million transistors [Mtransistors])            | 386   | 386   | 386   | 773   | 773   | 773   | 1546  | 1546  | 1546  |

| Chip size at introduction (mm²) ‡                                                  | 222   | 353   | 280   | 222   | 353   | 280   | 222   | 353   | 280   |

| Cost performance MPU (Mtransistors/cm² at introduction) (including on-chip SRAM) ‡ | 174   | 219   | 276   | 348   | 438   | 552   | 696   | 876   | 1,104 |

| Generation at production *                                                         | p04c  | p04c  | р07с  | р07с  | р07с  | p10c  | p10c  | p10c  | p13c  |

| Functions per chip at production (million transistors [Mtransistors])              | 193   | 193   | 386   | 386   | 386   | 773   | 773   | 773   | 1546  |

| Chip size at production (mm²) §§                                                   | 111   | 88    | 140   | 111   | 88    | 140   | 111   | 88    | 140   |

| Cost performance MPU (Mtransistors/cm² at production, including on-chip SRAM) ‡    | 174   | 219   | 276   | 348   | 438   | 552   | 696   | 876   | 1,104 |

Table 1h MPU (High-volume Microprocessor) Cost-Performance Product Generations and Chip Size Model—Long-term Years

| Year of Production                                                                  | 2014  | 2015  | 2016  | 2017  | 2018   | 2019   | 2020   |

|-------------------------------------------------------------------------------------|-------|-------|-------|-------|--------|--------|--------|

| DRAM ½ Pitch (nm) (contacted)                                                       | 28    | 25    | 22    | 20    | 18     | 16     | 14     |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm) (f)                                              | 28    | 25    | 22    | 20    | 18     | 16     | 14     |

| MPU Physical Gate Length (nm)                                                       | 11    | 10    | 9     | 8     | 7      | 6      | 6      |

| SRAM Cell (6-transistor) Area factor ++                                             | 104.1 | 103.4 | 102.8 | 102.2 | 101.7  | 101.3  | 100.9  |

| SRAM Cell (6-transistor) Area factor ++                                             | 104.1 | 103.4 | 102.8 | 102.2 | 101.7  | 101.3  | 100.9  |

| Logic Gate (4-transistor) Area factor ++                                            | 320   | 320   | 320   | 320   | 320    | 320    | 320    |

| Logic Gate (4-transistor) Area factor ++                                            | 320   | 320   | 320   | 320   | 320    | 320    | 320    |

| SRAM Cell (6-transistor) Area efficiency ++                                         | 0.63  | 0.63  | 0.63  | 0.63  | 0.63   | 0.63   | 0.63   |

| Logic Gate (4-transistor) Area efficiency ++                                        | 0.50  | 0.50  | 0.50  | 0.50  | 0.50   | 0.50   | 0.50   |

| SRAM Cell (6-transistor) Area ++                                                    | 0.084 | 0.066 | 0.052 | 0.041 | 0.032  | 0.026  | 0.020  |

| SRAM Cell (6-transistor) Area w/overhead ++                                         | 0.13  | 0.106 | 0.083 | 0.066 | 0.052  | 0.041  | 0.032  |

| Logic Gate (4-transistor) Area ++                                                   | 0.26  | 0.20  | 0.16  | 0.13  | 0.10   | 80.0   | 0.06   |

| Logic Gate (4-transistor) Area w/overhead ++                                        | 0.51  | 0.41  | 0.32  | 0.26  | 0.20   | 0.16   | 0.13   |

| Transistor density SRAM (Mtransistors/cm²)                                          | 4,484 | 5,687 | 7,208 | 9,130 | 11,558 | 14,625 | 18,497 |

| Transistor density logic (Mtransistors/cm²)                                         | 778   | 980   | 1,235 | 1,555 | 1,960  | 2,469  | 3,111  |

| Generation at introduction *                                                        | p16c  | p19c  | p19c  | p19c  | p22c   | p22c   | p22c   |

| Functions per chip at introduction (million transistors [Mtransistors])             | 3092  | 3092  | 3092  | 6184  | 6184   | 6184   | 12368  |

| Chip size at introduction (mm²) ‡                                                   | 222   | 353   | 280   | 222   | 353    | 280    | 222    |

| Cost performance MPU (Mtransistors/cm² at introduction) (including on-chip SRAM) ‡  | 1,391 | 1,753 | 2,209 | 2,783 | 3,506  | 4,417  | 5,565  |

| Generation at production *                                                          | p13c  | p13c  | p16c  | p16c  | p16c   | p19c   | p19c   |

| Functions per chip at production (million transistors [Mtransistors])               | 1546  | 1546  | 3092  | 3092  | 3092   | 6184   | 6184   |

| Chip size at production (mm²) §§                                                    | 111   | 88    | 140   | 111   | 88     | 140    | 111    |

| Cost performance MPU (Mtransistors/cm² at production, including on-<br>chip SRAM) ‡ | 1,391 | 1,753 | 2,209 | 2,783 | 3,506  | 4,417  | 5,565  |

#### Notes for Tables 1g and 1h:

++ The MPU area factors are analogous to the "cell area factor" for DRAMs. The reduction of area factors has been achieved historically through a combination of many factors, for example—use of additional interconnect levels, self-alignment techniques, and more efficient circuit layout. However, recent data has indicated that the improvement (reduction) of the area factors is slowing, and is virtually flat for the logic gate area factor.

‡ MPU Cost-performance Model—Cost-performance MPU includes Level 2 (L2) on-chip SRAM (512Kbyte/2000), and the combination of both SRAM and logic transistor functionality doubles every technology node cycle.

§§ MPU Chip Size Model—Both the cost-performance and high-performance MPUs InTER-generation production-level chip sizes are modeled to be below affordable targets, which are flat through 2020 (280 mm²/cost-performance at introduction; 140 mm²/cost-performance at production; 310 mm²/high-performance at production). The MPU flat chip-size affordability model is accomplished by doubling the on-chip functionality every technology cycle. Actual market chip sizes may exceed the affordability targets in order to continue the doubling of on-chip functionality on a shorter cycle, but their unit costs and market values must be increased. In the 2005 ITRS, the MPU model now includes introduction-level high-performance MPU targets that shrink to the "affordable" targets (the same way the DRAM model operates). The InTRA-generation chip size shrink model is 0.5× every two-year density-driven technology cycle through 2004, and then 0.5× every three-year density-driven technology cycle after 2004, in order to stay under the affordable flat-chip-size target.

Refer to the Glossary for definitions.

<sup>\*</sup> p is processor, numerals reflect year of production; c indicates cost-performance product. Examples—the cost-performance processor, p04c, was introduced in 2002, but not ramped into volume production until 2004; similarly, the p07c, is introduced in 2004, but is targeted for volume production in 2007.

Table 1i High-Performance MPU and ASIC Product Generations and Chip Size Model—Near-term Years

| Year of Production                                                                                         | 2005   | 2006  | 2007  | 2008  | 2009  | 2010  | 2011  | 2012  | 2013   |

|------------------------------------------------------------------------------------------------------------|--------|-------|-------|-------|-------|-------|-------|-------|--------|

| DRAM ½ Pitch (nm) (contacted)                                                                              | 80     | 70    | 65    | 57    | 50    | 45    | 40    | 36    | 32     |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm) (f)                                                                     | 90     | 78    | 68    | 59    | 52    | 45    | 40    | 36    | 32     |

| MPU Physical Gate Length (nm)                                                                              | 32     | 28    | 25    | 23    | 20    | 18    | 16    | 14    | 13     |

| Logic (Low-volume Microprocessor) High-perform                                                             | nance‡ |       |       |       |       |       |       |       |        |

| Generation at Introduction                                                                                 | p07h   | p10h  | p10h  | p10h  | p13h  | p13h  | p13h  | p16h  | p16h   |

| Functions per chip at introduction (million transistors)                                                   | 1106   | 2212  | 2212  | 2212  | 4424  | 4424  | 4424  | 8848  | 8848   |

| Chip size at introduction (mm²)                                                                            | 492    | 781   | 620   | 492   | 781   | 620   | 492   | 781   | 620    |

| Generation at production **                                                                                | p04h   | p04h  | p07h  | p07h  | p07h  | p10h  | p10h  | p10h  | p13h   |

| Functions per chip at production (million transistors)                                                     | 553    | 553   | 1106  | 1106  | 1106  | 2212  | 2212  | 2212  | 4424   |

| Chip size at production (mm²) §§                                                                           | 246    | 195   | 310   | 246   | 195   | 310   | 246   | 195   | 310    |

| High-performance MPU Mtransistors/cm² at introduction and production (including on-chip SRAM) ‡            | 225    | 283   | 357   | 449   | 566   | 714   | 899   | 1133  | 1427   |

| ASIC                                                                                                       |        | •     |       |       | •     |       |       |       |        |

| ASIC usable Mtransistors/cm² (auto layout)                                                                 | 225    | 283   | 357   | 449   | 566   | 714   | 899   | 1,133 | 1,427  |

| ASIC max chip size at production (mm²)<br>(maximum lithographic field size)                                | 858    | 858   | 858   | 858   | 858   | 858   | 858   | 858   | 858    |

| ASIC maximum functions per chip at production (Mtransistors/chip) (fit in maximum lithographic field size) | 1,928  | 2,430 | 3,061 | 3,857 | 4,859 | 6,122 | 7,713 | 9,718 | 12,244 |

Table 1j High-Performance MPU and ASIC Product Generations and Chip Size Model—Long-term Years

| Year of Production                                                                                               | 2014   | 2015   | 2016   | 2017   | 2018   | 2019   | 2020   |

|------------------------------------------------------------------------------------------------------------------|--------|--------|--------|--------|--------|--------|--------|

| DRAM ½ Pitch (nm) (contacted)                                                                                    | 28     | 25     | 22     | 20     | 18     | 16     | 14     |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm) (f)                                                                           | 28     | 25     | 22     | 20     | 18     | 16     | 14     |

| MPU Physical Gate Length (nm)                                                                                    | 11     | 10     | 9      | 8      | 7      | 6      | 6      |

| Logic (Low-volume Microprocessor) High-performance ‡                                                             |        |        |        |        |        | •      |        |

| Generation at Introduction                                                                                       | p16h   | p19h   | p19h   | p19h   | p22h   | p22h   | p22h   |

| Functions per chip at introduction (million transistors)                                                         | 8848   | 17696  | 17696  | 17696  | 35391  | 35391  | 35391  |

| Chip size at introduction (mm²)                                                                                  | 492    | 781    | 620    | 492    | 781    | 620    | 492    |

| Generation at production **                                                                                      | p13h   | p13h   | p16h   | p16h   | p16h   | p19h   | p19h   |

| Functions per chip at production (million transistors)                                                           | 4424   | 4424   | 8848   | 8848   | 8848   | 17696  | 17696  |

| Chip size at production (mm²) §§                                                                                 | 246    | 195    | 310    | 246    | 195    | 310    | 246    |

| High-performance MPU Mtransistors/cm² at introduction and production (including on-chip SRAM) ‡                  | 1798   | 2265   | 2854   | 3596   | 4531   | 5708   | 7192   |

| ASIC                                                                                                             |        |        |        |        | •      | •      |        |

| ASIC usable Mtransistors/cm² (auto layout)                                                                       | 1,798  | 2,265  | 2,854  | 3,596  | 4,531  | 5,708  | 7,192  |

| ASIC max chip size at production (mm²) (maximum<br>lithographic field size)                                      | 858    | 858    | 858    | 858    | 858    | 858    | 858    |

| ASIC maximum functions per chip at production<br>(Mtransistors/chip) (fit in maximum lithographic field<br>size) | 15,427 | 19,436 | 24,488 | 30,853 | 38,873 | 48,977 | 61,707 |

#### Notes for Tables 1i and 1j:

<sup>\*</sup> p is processor, numerals reflect year of production; c indicates cost-performance product. Examples—the cost-performance processor, p04c, was introduced in 2002, but not ramped into volume production until 2004; similarly, the p07c, is introduced in 2004, but is targeted for volume production in 2007.

<sup>‡</sup> MPU Cost-performance Model—Cost-performance MPU includes Level 2 (L2) on-chip SRAM (512Kbyte/2000), and the combination of both SRAM and logic transistor functionality doubles every technology cycle.

§§ MPU Chip Size Model—Both the cost-performance and high-performance MPUs InTER-generation production-level chip sizes are modeled to be below affordable targets, which are flat through 2020 (280 mm²/cost-performance at introduction; 140 mm²/cost-performance at production; 310 mm²/high-performance at production). The MPU flat chip-size affordability model is accomplished by doubling the on-chip functionality every technology cycle. Actual market chip sizes may exceed the affordability targets in order to continue the doubling of on-chip functionality on a shorter cycle, but their unit costs and market values must be increased. In the 2005 ITRS, the MPU model now includes introduction-level high-performance MPU targets that shrink to the "affordable" targets (the same way the DRAM model operates). The InTRA-generation chip size shrink model is 0.5×every two-year density-driven technology cycle after 2004, in order to stay under the affordable flat-chip-size target.

Refer to the Glossary for definitions.

# チップ・サイズ、リソグラフィ・フィールド、ウェーハ・サイズの各傾向

2年あるいは3年ごとに継続して素子寸法が約 30%縮小するにもかかわらず、IEEE (Institute of Electrical and Electronics Engineers: 米国電気電子学会)国際固体素子会議などの技術フォーラムにおいて先端メモリあるいはロジック製品の導入段階におけるサイズは、6 年ごとに倍増している(年間約 12%増)。(今までは、1.5~2 年ごとに機能が倍増する)ムーアの法則に従い、ビット/キャパシタ/トランジスタを年間 40-60%増の割合で収容するために、このチップ・エリヤの増加が必要となる。しかしながら、先端製品のコスト/機能が年間~30%縮小するという今までの傾向を維持するには、設備生産性の増強、製造歩留りの向上、最大サイズ・ウェーハの使用、ウェーハとシリコン面積の維持あるいは増加、とりわけ、1枚のウェーハ上の使用可能な機能単位(トランジスタ、ビット、ロジックのゲート)あるいはチップ数の増加が継続的に必要となる。

1枚のウェーハ上の使用可能な機能単位、チップ総数の増加は、主として素子サイズの小型化(縮小/スケーリング) と製品/プロセスの再設計(圧縮)の組合せにより達成される。たとえば、最新の ITRS チップサイズモデルを使って、低コスト製品世代[世代間(世代対世代)機能を 2年ごとに倍増]の初期のチップ・サイズは一定のままにとどまるか、可能な限り維持することが予測されている。さらに、各技術サイクル期間で、世代内(世代の中)年間縮小比率 50%(0.7×のリソグラフィ縮小比率の二乗)でチップ・サイズを縮小することが必要となっており、またあるいはデザイン要求に関係ある密度の改善が可能であるのならばこの値は加速される。

手ごろな値段で購入できる DRAM やフラッシュメモリ製品でも、世代内で仮想的にチップ・サイズを一定に維持するために、トータル・チップ・エリヤの 58-63%というセル・エリヤ・アレイ効率も維持しなければならない。歴史的にDRAM やフラッシュメモリ製品はセル・エリヤ・デザイン・ファクタ(a) (最小機能サイズの二乗で表したセル・エリヤ (Ca=af²))を小さくすることが必要となる。PIDS と FEP ITWG はアレイ効率目標、セルエリアファクター、およびチップあたりのビット数のメンバー調査データを提供している。さらにフロントエンド・プロセスの章に、セル・エリヤ目標を達成する解決策へのチャレンジとニーズが詳述されている。これら新しいチャレンジを追尾(tracking) /調整することが非常に重要なので、DRAM とフラッシュメモリのセル・エリヤ・ファクタ、目標エリヤ・サイズ、トータル・チップ・サイズに対するセル・アレイ・エリヤの割合などの項目は ORTCTable 1c、1d、1e、1f にて追尾を継続していくこととなる(詳細については、用語集参照)。

特に最新の調査データと入手可能な公開された情報は、2005 年 ITRS における DRAM セルエリアファクターのリダクションレートが再度著しく遅くなっていることを示している。例えば DRAM の 7 あるいは 7.5 というデザインファクターは短期からはなくなり、5 は長期から完全に消えた。6 という値だけが 2008 年に始まり、2005 年 ITRS の最終年である 2020 年まで残っている。さらに 2003 年 ITRS の 68%というアグレッシブな DRAM のセルエリア効率は、2008 年に始まる 56%に後退した。この縮小化された DRAM 製品の機能密度の生産性は、DRAM の"Moore s Law"が示すチップあたりのビット数のターゲットが短期、及び長期のいずれにおいても 3 年で 2 倍に減速されることを必要とし、64G ビット DRAM 製品は、2020 年という今回の ITRS における最終年よりも先に延びることになる。(Figure9、10 の Function Size and Functions per Chip 参照。)

新しい 2005 年の ORTC フラッシュ製品モデルでは、機能ビットサイズは歴史的にそのデザインファクターの縮小化、及びコンタクトのないポリシリコンの密なライン間の幅のスケーリングを加速してきた。急激なスケーリングのサイクル、及びデザインファクターの縮小化(~4)により、フラッシュのチップサイズモデルは歴史的に機能(ビットサイズ)に必要な面積の低減の加速をもたらした。その結果として、フラッシュのコンタクトのないポリシリコンハーフピッチは、DRAMのジグザグにコンタクトされた(stagger-contacted) M1 ハーフピッチとクロスオーバーした。しかしながらリソグラフィ TWGによれば、最先端のフラッシュ製造技術はまだ最先端の DRAM 製造にひつようなプロセス装置と同様である。しかしながら、DRAM 製品に使われるのと同じ能力のリソグラフィ装置を使えば、セル面積の更なる縮小化は可能である。

フラッシュのシングルレベルセル(SLC)ビット技術は、2005 年にすばやく 76nm のコンタクトのないポリシリコンハーフピッチと、"4"というデザインファクターを実現し、その結果としてフラッシュのビットセル面積は DRAM のサイズの半分となり(2005 年 ITRS の Figure Product Function Chip Trends 参照)、DRAM 製品では未だ 1Gbit に過ぎない 2005 年に、144mm<sup>2</sup>で 4Gbit の SLC 製品の生産を可能としている。(1Gbit の DRAM の方がチップサイズは縮小化されているにもかかわらず。)さらにフラッシュメモリ技術は、同じ面積で電気的にビットの数を倍増することができ、結果として実質的なチップあたりのビット数が倍増された、140mm<sup>2</sup>で 8Gbit の最初の製品を実現している。

2001年のITRS には、設計 ITWG により MPU チップ・サイズ・モデルが改良されて、最新のトランジスタ密度、大型オンチップ SRAM、小型目標チップ・サイズで MPU チップ・サイズ・モデルがアップデートされた。もともとの設計 ITWG では、トランジスタ設計改善ファクタを含む追加詳細項目がモデルに追加されてもいる。設計 ITWG は、SRAMトランジスタの設計改善は、スローペースで行われており、ロジック・ゲート・トランジスタでは設計改善が殆ど行われていないと述べている。ほとんど全ての「縮小」と密度改善はリソグラフィにより可能となった配線ハーフピッチのスケーリングによりもたらされている。

今回の 2005 年 ITRS の MPU モデルは、2000/180nm(もともとは 1999/180nm)に始まる 2001 年ITRS と変わりがなく、引き続き高性能 MPU(310mm2)およびコスト-性能 MPU(140mm2)双方におけるチップ・サイズ維持の傾向を考慮し、手ごろな値段と電力管理についての競争的な要求を反映している。 2004 年までの MPU 2 年サイクル・ハーフピッチ「追いつきフェーズ」により、リソグラフィの改善だけで MPU 製品は一定のチップ・サイズを保つことができる。 しかし 2004 年以降、ITRS の技術世代に示されている世代間 MPU チップ・サイズのモデルでは、各テクノロジサイクルごとにオンチップ・トランジスタの数を倍増させるペースを減速させることによってのみ、一定にとどめることができる。 Figure9、10の Function Size and Functions per Chip 参照。

3 年テクノロジサイクルに予測された結果により、現在の MPU チップ・サイズ・モデルは、オンチップ・トランジスタに関するムーアの法則の割合を3年ごとに倍増へと低下させる。チップ・サイズ一定の目標を達成しかつ2年ごとにオンチップ機能(トランジスタ)倍増という今までの傾向を達成するためには、MPU のチップ設計者およびプロセス設計者は、基本的なリソグラフィ・ベース型スケーリング傾向に設計/プロセスの改善を追加しなければならない。Table1g、1h、1i、1jに MPU モデルの新しい目標値を要約して示す。

生産性を向上するには、製作プロセスの各ステップで良好なチップの生産量を増加しなければならない。1回の露光で複数チップをプリントする能力は主な生産性の原動力であり、その原動力はリソグラフィ・ツールのフィールド・サイズ、およびウェーハにプリントされるチップのサイズとアスペクト比により決定されている。今までのリソグラフィ露光フィールドは、2世代のテクノロジ・サイクルドごとに倍増してチップ・サイズ増大の需要を満たしていた。その結果、非常に広いステップ走査フィールド(26 X 33 = 858mm²)が達成された。

しかし、リソグラフィ ITWG により、継続的に解像力の向上を図りながら大きなフィールドサイズを保つことは、大幅なコスト上昇を招ことが示された。そのためリソグラフィ ITWG の提示するロードマップは、最大フィールドサイズとより代表的な可能なフィールドサイズについての要求を満足するために、個々のメモリとロジック製品のチップサイズモデルに依存することになる。

### 18 総括ロードマップ技術指標 (ORTC)

DRAM チップ・サイズは、歴史的に最も困難な露光ハーフピッチと、受け入れ可能なリソグラフィ・フィールド・サイズを最も適切に示すと見なされていた。2005 年の ITRS の DRAM チップ・サイズ・モデルでは、導入レベルのチップ・サイズを 704mm²リソグラフィ・フィールドよりも小さくして、少なくとも 1 個の導入レベル・チップ・サイズがフィールド内に収まるようにしている。今回の 2005 年 ITRS の生産レベル DRAM モデル(140mm2 より小さいチップ・サイズ維持を目標)では、少なくとも 4 個の導入レベル・チップ・サイズを 572mm²のフィールド内に収めている。

テクノロジ世代のスケーリングとセル設計改善(A ファクタの縮小)との組合せにより、2 年ごとにオンチップ・ビットの倍増を果たしながら、この目標を達成することが可能となる。しかし上記の生産レベルチップサイズモデルで記述したように、DRAM 設計改善スピードの低下により、入手可能なチップサイズ、あるいはリソグラフィ・フィールドの限界内にとどめるために、追加するオンチップ・ビット数を減らすという要求がもたらされている。これは、現在の DRAM モデルでムーアの法則が示すビット/チップ・レートを 2 倍/3 年へと下げることにより達成することができる。DRAM モデルのデタ目標を Table1 c、1 d、1e、1f に載せる。

最大リソグラフィ・フィールドサイズの絶対値は、高性能 MPU や ASIC の初期導入時のチップサイズによってドライブされる。このサイズは、リソグラフィ TWG による最大入手可能サイズ(26 X 33 = 858mm²)と等しくなる。将来、8 X ともなるマスク倍率レベルは、最大フィールドサイズを現在の 858mm²から 1/4 に、すなわち 858mm²に引き下げられることが予想される。最大フィールドサイズの限界と、マスク倍率の関する課題に関連する詳細は、リソグラフィ TWG により、リソグラフィの章の中で示される。最大リソグラフィ・フィールドサイズは、Table2a と b に示した。

2005 年 ITRS における DRAM モデル、フラッシュメモリモデル、及び MPU モデルは、DRAM と MPU の設計およびプロセスの改善目標を達成できるかどうかにかかっている。達成できない場合は、現在のロードマップが示したのより大きなチップ・サイズをプリントする方向への圧力が高まるか、または、オンチップ機能に関する"Moore's Law"のレートがさらに低下する。いずれの結果でも、コスト機能の縮小レート(半導体産業の生産性向上と競争力に関するクラシカルな尺度(classical measure)) にマイナスのインパクトをもたらすことになる。

コスト削減の圧力が高まる中で、特に先端的な段階にある製造業者にとって 300 mm の生産性を押し上げるニーズが急速に増大していくことになる。しかし、経済情勢の悪化は課題をもたらし、設備投資を抑制してきた。2001 年版ウェーハ直径世代ロードマップ(Table 2a, 2b を参照、さらに詳細はフロントエンドプロセスの章に)では、2001 年初めに 300 mm 能力の立上げで意見が一致している。また、現ロードマップでは、次の 450 mm 径へ 1.5 倍ウェーハ・サイズを大きくすることは現在のロードマップでは 2012 年までに必要になるとは期待されていない。しかし、他の生産性を向上させる原動力(リソグラフィおよび設計/プロセスの改善)がスケジュール通りに実現しなかった場合、生産性の向上として大直径ウェーハの使用を加速するか他の同等の効果のあるプロセス改善をしなければならないだろう。

将来技術の加速/減速の影響、および次のウェーハ世代への転換のタイミングにより、包括的な長期的な工場の生産性および産業経済モデルの開発と適用が必要となる。現在、SEMI (Semiconductor Equipment and Materials Institute: 米国半導体装置材料規格委員会)と SEMATECH (Semiconductor Manufacturing Technology Institute: 半導体製造技術研究所)が合同でこのような産業経済モデル化 (industry economic modeling: IEM)の作業を後援し、実行している。最も確かなのは、将来の技術的・経済的必要性を明確にするとともに、必要とされる研究と開発に対する適切な投資メカニズムを導き出すために、半導体サプライヤと生産者との間でのプレコンペティティブな協力が必要であるということである。

Year of Production DRAM ½ Pitch (nm) (contacted) MPU/ASIC Metal 1 (M1) ½ Pitch (nm) (f) MPU Physical Gate Length (nm) Lithography Field Size Maximum Lithography Field Size—area (mm²) Maximum Lithography Field Size—length Maximum Lithography Field Size—width (mm) Maximum Substrate Diameter (mm)-Highvolume Production (>20K wafer starts per month) Bulk or epitaxial or SOI wafer

Table 2a Lithographic-Field and Wafer-Size Trends—Near-term Years

Table 2b Lithographic-Field and Wafer Size Trends—Long-term Years

| Year of Production                                                                      | 2014 | 2015 | 2016 | 2017 | 2018 | 2019 | 2020 |

|-----------------------------------------------------------------------------------------|------|------|------|------|------|------|------|

| DRAM ½ Pitch (nm) (contacted)                                                           | 28   | 25   | 22   | 20   | 18   | 16   | 14   |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm) (f)                                                  | 28   | 25   | 22   | 20   | 18   | 16   | 14   |

| MPU Physical Gate Length (nm)                                                           | 11   | 10   | 9    | 8    | 7    | 6    | 6    |

| Lithography Field Size                                                                  |      |      |      |      |      |      |      |

| Maximum Lithography Field Size—area (mm²)                                               | 858  | 858  | 858  | 858  | 858  | 858  | 858  |

| Maximum Lithography Field Size—length (mm)                                              | 33   | 33   | 33   | 33   | 33   | 33   | 33   |

| Maximum Lithography Field Size—width (mm)                                               | 26   | 26   | 26   | 26   | 26   | 26   | 26   |

| Maximum Substrate Diameter (mm)—High-volume<br>Production (>20K wafer starts per month) |      |      |      |      |      |      |      |

| Bulk or epitaxial or SOI wafer                                                          | 450  | 450  | 450  | 450  | 450  | 450  | 450  |

# パッケージされたチップの性能

### パッド数とピン数、パッドピッチ、ピン当たりコスト、周波数

シングルチップのより高い機能への要求は、各製品世代に対するトランジスタ数またはビット(メモリセル)数の集積化を要求する。典型的には、チップのトランジスタ数の増加と同様に、入出力(I/O)信号を集積回路に導入するのに必要なパッド数もピン数も増加する(Table3a、3b 参照)。

付加的な電源・グランドのチップへの接続は、熱設計の最適化とノイズ低減に必要である。テスト ITWG から提供されたチップパッド数に基づくと、MPU や高性能 ASIC などのロジック製品は、ITRS 期間の間に 4-6k パッドになる。MPU 製品は全パッド数がこの期間に約 50%増加し、ASIC は最大パッド数が 2 倍になると予測される。これらの 2 タイプの製品は、電源/グランドパッドの割合が実質的に異なっている。 典型的な MPU 製品は、パッド数の 1/3 が入出力信号であり、2/3 が電源・グランドである。 つまり、入出力パッド 1 ヶに対して、2 ヶの電源・グランドを持っている。 MPU とは異なり、高性能 ASIC 製品は、典型的には入出力パッド 1 ヶに対して、1 ヶの電源・グランドを持っている。

| Year of Production                                                | 2005      | 2006    | 2007         | 2008         | 2009         | 2010         | 2011     | 2012         | 2013         |

|-------------------------------------------------------------------|-----------|---------|--------------|--------------|--------------|--------------|----------|--------------|--------------|

| DRAM ½ Pitch (nm) (contacted)                                     | 80        | 70      | 65           | 57           | 50           | 45           | 40       | 36           | 32           |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm) (f)                            | 90        | 78      | 68           | 59           | 52           | 45           | 40       | 36           | 32           |

| MPU Physical Gate Length (nm)                                     | 32        | 28      | 25           | 23           | 20           | 18           | 16       | 14           | 13           |

| Number of Chip I/Os (Number of Total Chip Pag                     | ls)—Maxim | um      |              |              |              |              |          |              |              |

| Total pads—MPU                                                    | 3,072     | 3,072   | 3,072        | 3,072        | 3,072        | 3,072        | 3,072    | 3,072        | 3,072        |

| Signal I/O—MPU (1/3 of total pads)                                | 1,024     | 1,024   | 1,024        | 1,024        | 1,024        | 1,024        | 1,024    | 1,024        | 1,024        |

| Power and ground pads—MPU<br>(2/3 of total pads)                  | 2,048     | 2,048   | 2,048        | 2,048        | 2,048        | 2,048        | 2,048    | 2,048        | 2,048        |

| Total pads—ASIC high-performance                                  | 4,000     | 4,200   | 4,400        | 4,400        | 4,600        | 4,800        | 4,800    | 5,000        | 5,400        |

| Signal I/O pads—ASIC high-performance                             | 2,000     | 2,100   | 2,200        | 2,200        | 2,300        | 2,400        | 2,400    | 2,500        | 2,700        |

| Power and ground pads—ASIC high-<br>performance (½ of total pads) | 2,000     | 2,100   | 2,200        | 2,200        | 2,300        | 2,400        | 2,400    | 2,500        | 2,700        |

| Number of Total Package Pins—Maximum [1]                          |           |         |              |              |              |              |          |              |              |

| Microprocessor/controller, cost-performance                       | 550-900   | 550–990 | 600-<br>1088 | 600–<br>1198 | 660-<br>1318 | 660-<br>1450 | 720-1596 | 720-<br>1754 | 800-<br>1930 |

| Microprocessor/controller, high-performance                       | 900       | 990     | 1088         | 1198         | 1318         | 1450         | 1596     | 1754         | 1930         |

| ASIC (high-performance)                                           | 3000      | 3180    | 3371         | 3573         | 3787         | 4015         | 4256     | 4511         | 4736         |

Table 3a Performance of Packaged Chips: Number of Pads and Pins—Near-term Years

#### Tables 3a and 3b の注記

[1] ピン数は、PWB 技術とシステムコストによって、狭ピッチ格子接続が使用される幾つかの応用分野によって限られる。結 果として、最多ピン数用途は、より大きなパッケージサイズを使用する。信号ピン比率の関係は用途に依存し、2:1 から 1:4 へと予想された範囲内で大きく変化する。

| Year of Production                                            | 2014     | 2015     | 2016     | 2017     | 2018     | 2019      | 2020      |

|---------------------------------------------------------------|----------|----------|----------|----------|----------|-----------|-----------|

| DRAM ½ Pitch (nm) (contacted)                                 | 28       | 25       | 22       | 20       | 18       | 16        | 14        |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm) (f)                        | 28       | 25       | 22       | 20       | 18       | 16        | 14        |

| MPU Physical Gate Length (nm)                                 | 11       | 10       | 9        | 8        | 7        | 6         | 6         |

| Number of Chip I/Os (Number of Total Chip Pads)—Ma            | aximum   |          |          |          |          |           |           |

| Total pads—MPU                                                | 3,072    | 3,072    | 3,072    | 3,072    | 3,072    | 3,072     | 3,072     |

| Signal I/O—MPU (1/3 of total pads)                            | 1,024    | 1,024    | 1,024    | 1,024    | 1,024    | 1,024     | 1,024     |

| Power and ground pads—MPU<br>(2/3 of total pads)              | 2,048    | 2,048    | 2,048    | 2,048    | 2,048    | 2,048     | 2,048     |

| Total pads—ASIC high-performance                              | 5,400    | 5,600    | 6,000    | 6,000    | 6,200    | 6,200     | 6,200     |

| Signal I/O pads—ASIC high-performance                         | 2,700    | 2,800    | 3,000    | 3,000    | 3,100    | 3,100     | 3,100     |

| Power and ground pads—ASIC high-performance (½ of total pads) | 2,700    | 2,800    | 3,000    | 3,000    | 3,100    | 3,100     | 3,100     |

| Number of Total Package Pins—Maximum [1]                      |          |          |          |          |          |           |           |

| Microprocessor/controller, cost-performance                   | 800-2124 | 880-2336 | 880-2568 | 960-2824 | 960-3108 | 1050-3418 | 1050-3760 |

| Microprocessor/controller, high-performance                   | 2124     | 2336     | 2568     | 2824     | 3108     | 3418      | 3760      |

| ASIC (high-performance)                                       | 4973     | 5222     | 5483     | 5757     | 6045     | 6347      | 6665      |

Table 3b Performance of Packaged Chips: Number of Pads and Pins—Long-term Years

A&P ITWG から提供されたパッケージピン数(Table3a、3b)とピン当たりコスト(Table4a、4b)は、将来的の製造 経済学への挑戦を指摘している。チップ当たりのトランジスタ数の増加予測に基づくと、パッケージピン数(ボー ル数)は年率約 10%で増加し、ピン当たりコストは年率5%で減少すると予想される。これらのトレンドにより、パッ ケージング技術のサプライヤにとっては、低コスト解を提供する事がより困難になる。何故ならば、パッケージン グ全般における平均コストは年率 5%で増加するからである(0.95cost/pin×1.10pins/year = 1.05cost/year)。

非常に競争の激しいコンシューマ電子機器環境においては、パソコンや携帯電話のような大規模なハイテク 製品の価格は、現状維持か、減少傾向となる。これらのハイテク製品は典型的には2年毎に2倍の性能を提供 している。これは最先端半導体製造メーカの最終用途市場環境であり、機能(ビット、トランジスタ)当たりコストの 年率 30%またはそれ以上の低減(同じ価格で、2 年毎にチップ当たりの機能性は 2 倍 = 29%/year)の ITRS 経済的要求に従う、基本的な経済的牽引車である。

もし、将来の半導体素子製品の価格を維持もしくは低下することを目標とし、また、平均のピン当たりコストが 5%しか削減出来ない時に、ユニット当たりの平均ピン数が 10%増加するとした場合、次のようになる。

- 1. 全製品コストに占める平均パッケージングコストの割合は、15年間のロードマップ期間に倍増する。

- 2. その結果は総収益マージンを大幅に減少させ、研究開発/工場生産能力への投資能力の制限となる。

この結論が、マルチチップ・モジュールやバンプ型チップ・オン・ボード(Chip-on-Board: COB)やその他の創造的な解決策の使用によるシステム・オン・チップ(System-on-Chip: SoC)への機能統合より、全体のシステムのピン数要求を低減させる業界傾向の原動力の1つとなっている。

機能当たりのコストを指数的に削減しながら機能性を増加するニーズに加えて、高性能低コスト型製品への市場要求も存在する。消費者の要求を満たすために  $1.5 \sim 2$  年毎にチップ当たりの機能が倍増するというムーアの法則が予測するように、ますます高スピードで電気信号を処理したいという要求も存在する。MPU の場合、今までプロセッサの命令数/秒も  $1.5 \sim 2$  年ごとに倍増している。MPU 製品について、百万命令/秒 (millions of instructions per second: MIPs)の単位で測定される処理能力の増加は、「本質の技術性能」(クロック・間波数)×「アーキテクチャ性能」(クロック・サイクル毎の命令)の組合せで達成される。ますます高くなる動作周波数へのニーズは、新規のプロセス、設計、パッケージング技術の開発を継続的に要求していく。

最大オン・チップ (on-chip) 周波数と最大チップ・ツー・ボード (chip-to-board) 周波数の動向を予測するため、設計 ITWG およびアセンブリ&パッケージ ITWG から提供された行項目を含む Table4c、4d には、上記の考慮が反映されている。各製品世代で入手可能な最大周波数は、固有トランジスタ性能(オン・チップ、ローカル・クロック)に直接関係している。ライン・ツー・ライン (line-to-line) およびライン・ツー・サブストレート (line-to-substrate) の容量結合がもたらす信号伝播遅延の劣化により、チップを横切って伝播する信号の周波数とこの「ローカル」 周波数との差が拡大している。他の信号劣化はワイヤ・ボンドおよびパッケージ・リードのインダクタンスに関連している。パッケージがもたらす寄生効果を排除する唯一の実行可能な手段は、チップの直接取り付けであるう。チップ全体の信号とパワーの分布を最適化するため、配線層数が今後も増加することが予測される。配線のダウン・スケーリングも継続するので、銅配線 (低抵抗率) および低誘電率 (κ~2-3)を持つ様々な層間絶縁材料が、チップ製造工程において幅広く採用されるだろう。チップ・ツー・ボード動作周波数 (オフ・チップ)を上げるために、多重化手法も使用されるだろう。

Table 4a Performance and Package Chips: Pads, Cost—Near-term Years

| =                                                                                                                |          |          |          |          |         |        |         |        |          |

|------------------------------------------------------------------------------------------------------------------|----------|----------|----------|----------|---------|--------|---------|--------|----------|

| Year of Production                                                                                               | 2005     | 2006     | 2007     | 2008     | 2009    | 2010   | 2011    | 2012   | 2013     |

| DRAM ½ Pitch (nm) (contacted)                                                                                    | 80       | 70       | 65       | 57       | 50      | 45     | 40      | 36     | 32       |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm) (f)                                                                           | 90       | 78       | 68       | 59       | 52      | 45     | 40      | 36     | 32       |

| MPU Physical Gate Length (nm)                                                                                    | 32       | 28       | 25       | 23       | 20      | 18     | 16      | 14     | 13       |

| Chip Pad Pitch (micron)                                                                                          |          |          |          |          |         |        |         |        |          |

| Pad pitch—ball bond                                                                                              | 35       | 35       | 30       | 30       | 25      | 25     | 25      | 20     | 20       |

| Pad pitch—wedge bond                                                                                             | 30       | 25       | 25       | 25       | 20      | 20     | 20      | 20     | 20       |

| Pad Pitch—area array flip-chip (cost-<br>performance, high-performance)                                          | 150      | 130      | 120      | 110      | 100     | 90     | 90      | 90     | 90       |

| Pad Pitch—2-row staggered-pitch (micron)                                                                         | 45       | 40       | 35       | 35       | 35      | 35     | 35      | 35     | 35       |

| Pad Pitch—Three-tier-pitch pitch (micron)                                                                        | 45       | 40       | 35       | 35       | 35      | 35     | 35      | 35     | 35       |

| Cost-Per-Pin                                                                                                     |          |          |          |          |         |        |         |        |          |

| Package cost (cents/pin) (Cost per Pin Minimum<br>for Contract Assembly – Cost-performance) —<br>minimum—maximum | .58–1.17 | .57–1.11 | .64–1.05 | .63–1.00 | .62–.96 | 0.6194 | .60–.92 | 0.5890 | 0.57–.89 |

| Package cost (cents/pin) (Low-cost, hand-held<br>and memory) — minimum–maximum                                   | .2750    | .26–.49  | .25–.48  | .24–.47  | .23–.46 | .2245  | .21–.43 | .2042  | .20–.41  |

Table 4b Performance and Package Chips: Pads, Cost—Long-term Years

| Year of Production                                                                                                | 2014     | 2015     | 2016     | 2017     | 2018    | 2019     | 2020     |

|-------------------------------------------------------------------------------------------------------------------|----------|----------|----------|----------|---------|----------|----------|

| DRAM ½ Pitch (nm) (contacted)                                                                                     | 28       | 25       | 22       | 20       | 18      | 16       | 14       |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm) (f)                                                                            | 28       | 25       | 22       | 20       | 18      | 16       | 14       |

| MPU Physical Gate Length (nm)                                                                                     | 11       | 10       | 9        | 8        | 7       | 6        | 6        |

| Chip Pad Pitch (micron)                                                                                           |          |          |          |          |         |          |          |

| Pad pitch—ball bond                                                                                               | 20       | 20       | 20       | 20       | 20      | 20       | 20       |

| Pad pitch—wedge bond                                                                                              | 20       | 20       | 20       | 20       | 20      | 20       | 20       |

| Pad Pitch—area array flip-chip (cost-performance,<br>high-performance)                                            | 80       | 80       | 80       | 80       | 70      | 70       | 70       |

| Pad Pitch—2-row staggered-pitch (micron)                                                                          | 35       | 35       | 35       | 35       | 35      | 35       | 35       |

| Pad Pitch—Three-tier-pitch pitch (micron)                                                                         | 35       | 35       | 35       | 35       | 35      | 35       | 35       |

| Cost-Per-Pin                                                                                                      |          |          |          |          |         |          |          |

| Package cost (cents/pin) (Cost per Pin Minimum for<br>Contract Assembly – Cost-performance) — minimum—<br>maximum | 0.56–.87 | 0.55–.85 | 0.54–.83 | 0.53–.81 | 0.5280  | 0.51–.79 | 0.50–.79 |

| Package cost (cents/pin) (Low-cost, hand-held and<br>memory) — minimum—maximum                                    | .20–.39  | .19–.38  | .19–.37  | .18–.36  | .18–.35 | .18–.34  | .17–.34  |

Table 4c Performance and Package Chips: Frequency On-chip Wiring Levels—Near-term Years

| Year of Production                                                             | 2005  | 2006  | 2007  | 2008   | 2009   | 2010   | 2011   | 2012   | 2013   |  |  |

|--------------------------------------------------------------------------------|-------|-------|-------|--------|--------|--------|--------|--------|--------|--|--|

| DRAM ½ Pitch (nm) (contacted)                                                  | 80    | 70    | 65    | 57     | 50     | 45     | 40     | 36     | 32     |  |  |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm) (f)                                         | 90    | 78    | 68    | 59     | 52     | 45     | 40     | 36     | 32     |  |  |

| MPU Physical Gate Length (nm)                                                  | 32    | 28    | 25    | 23     | 20     | 18     | 16     | 14     | 13     |  |  |

| Chip Frequency (MHz)                                                           |       |       |       |        |        |        |        |        |        |  |  |

| On-chip local clock [1]                                                        | 5,204 | 6,783 | 9,285 | 10,972 | 12,369 | 15,079 | 17,658 | 20,065 | 22,980 |  |  |

| Chip-to-board (off-chip) speed (high-<br>performance, for peripheral buses)[2] | 3,125 | 3,906 | 4,883 | 6,103  | 7,629  | 9,536  | 11,920 | 14,900 | 18,625 |  |  |

| Maximum number wiring levels—maximum [3]                                       | 15    | 15    | 15    | 16     | 16     | 16     | 16     | 16     | 17     |  |  |

| Maximum number wiring levels—minimum [3]                                       | 11    | 11    | 11    | 12     | 12     | 12     | 12     | 12     | 13     |  |  |

Table 4d Performance and Package Chips: Frequency On-chip Wiring Levels—Long-term Years

| Year of Production                                                          | 2014   | 2015   | 2016   | 2017   | 2018   | 2019   | 2020   |

|-----------------------------------------------------------------------------|--------|--------|--------|--------|--------|--------|--------|

| DRAM ½ Pitch (nm) (contacted)                                               | 28     | 25     | 22     | 20     | 18     | 16     | 14     |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm) (f)                                      | 28     | 25     | 22     | 20     | 18     | 16     | 14     |

| MPU Physical Gate Length (nm)                                               | 11     | 10     | 9      | 8      | 7      | 6      | 6      |

| Chip Frequency (MHz)                                                        |        |        |        |        |        |        |        |

| On-chip local clock [1]                                                     | 28,356 | 33,403 | 39,683 | 45,535 | 53,207 | 62,443 | 73,122 |

| Chip-to-board (off-chip) speed (high-performance, for peripheral buses) [2] | 23,282 | 29,102 | 36,378 | 45,472 | 56,840 | 71,051 | 88,813 |

| Maximum number wiring levels—maximum [3]                                    | 17     | 17     | 17     | 18     | 18     | 18     | 18     |

| Maximum number wiring levels—minimum [3]                                    | 13     | 13     | 13     | 14     | 14     | 14     | 14     |

#### Tables 4c and 4d の注記

- [1] オンチップ周波数は基本的なトランジスタ遅延(PIDS TWG より提供)に基づいており、2007 年初期には 12 ヶのインバータの最大数が遅延する。2007 年以降は、PIDS モデルではトランジスタ遅延は約 14.7%の基本的な減少率となり、2020 年までオンチップ周波数は約 17.2%の成長率となる。

- [2] A&P モデルにより定義されるように、オフチップ周波数は 2017 年まで 25%の成長率で増加し、オンチップ周波数と交差する。多数の低速ピンと結合して使用される、小数の高速ピンのために、オフチップ周波数は増加すると期待される。

- [3] 配線数の最小値は接続メタル数を表し、最大値は更にパワー、グランド、信号調整、受動素子(例えば、キャパシタ)集積などの追加配線層数を含んでいる。

# 電気的な欠陥密度

DRAM、MPU、ASIC の電気的欠陥の密度に関する(量産の年に83~89.5 %のチップ歩留を達成するのに必要な) 最新目標を Table5a、5b に示す。 DRAM とマイクロプロセッサについて Table1 で報告したように、最新チップ寸法モデルに基づき異なるチップ寸法を考慮して、許容可能な欠陥数を計算している。 その上、図表内のデータは生産ライフサイクルの内量産レベルだけが報告されている。 歩留向上についての章に載せた式を使用して、同一技術ノードでの異なるチップ寸法における他の欠陥密度を計算することが出来る。 常に増加しているプロセス複雑性の指標として、ロジック・デバイス用マスク層の概数を載せている。

| Year of Production                                                                          | 2005  | 2006       | 2007  | 2008  | 2009  | 2010  | 2011  | 2012  | 2013  |

|---------------------------------------------------------------------------------------------|-------|------------|-------|-------|-------|-------|-------|-------|-------|

| DRAM ½ Pitch (nm) (contacted)                                                               | 80    | 70         | 65    | 57    | 50    | 45    | 40    | 36    | 32    |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm) (f)                                                      | 90    | <i>7</i> 8 | 68    | 59    | 52    | 45    | 40    | 36    | 32    |

| MPU Physical Gate Length (nm)                                                               | 32    | 28         | 25    | 23    | 20    | 18    | 16    | 14    | 13    |

| DRAM Random Defect $D_0$ at production chip size and 89.5% yield (faults/m <sup>2</sup> ) § | 3,517 | 2,216      | 2,791 | 3,516 | 2,215 | 2,791 | 3,516 | 2,215 | 2,791 |

| MPU Random Defect $D_0$ at production chip size and 83% yield (faults/ $m^2$ ) §§           | 1,757 | 2,214      | 1,395 | 1,757 | 2,214 | 1,395 | 1,757 | 2,214 | 1,395 |

| # Mask Levels—MPU                                                                           | 33    | 33         | 33    | 35    | 35    | 35    | 35    | 35    | 37    |

| # Mask Levels—DRAM                                                                          | 24    | 24         | 24    | 24    | 24    | 26    | 26    | 26    | 26    |

Table 5a Electrical Defects—Near-term Years

Table 5b Electrical Defects—Long-term Years

| Year of Production                                                                          | 2014  | 2015  | 2016  | 2017  | 2018  | 2019  | 2020  |

|---------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|

| DRAM ½ Pitch (nm) (contacted)                                                               | 28    | 25    | 22    | 20    | 18    | 16    | 14    |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm) (f)                                                      | 28    | 25    | 22    | 20    | 18    | 16    | 14    |

| MPU Physical Gate Length (nm)                                                               | 11    | 10    | 9     | 8     | 7     | 6     | 6     |

| DRAM Random Defect $D_0$ at production chip size and 89.5% yield (faults/m <sup>2</sup> ) § | 3,516 | 2,215 | 2,791 | 3,516 | 2,215 | 2,791 | 3,516 |

| MPU Random Defect $D_0$ at production chip size and 83% yield $(faults/m^2)$ §§             | 1,757 | 2,214 | 1,395 | 1,757 | 2,214 | 1,395 | 1,757 |

| # Mask Levels—MPU                                                                           | 37    | 37    | 37    | 39    | 39    | 39    | 39    |

| # Mask Levels—DRAM                                                                          | 26    | 26    | 26    | 26    | 26    | 26    | 26    |

Notes for Tables 5a and 5b:

$D_0$  — defect density

§ DRAM Model—Cell Area Factor (design/process improvement) targets are as follows:

$1999-2007/8 \times$ :  $2008-2020/6 \times$ . Due to the elimination of the "7.5," "7," and the "5" DRAM Cell design improvement Factors [a] in the latest 2005 ITRS DRAM consensus model, the addition of "Moore's Law" bits/chip slows from  $2 \times$  every 2.5–3 years to  $2 \times$  every three years.

DRAM product generations were increased by  $4 \times bits$ /chip every four years with interim  $2 \times bits$ /chip generation. However, in the latest model 2005 ITRS timeframe:

- 1. at the Introduction phase, after the 16 Gbit generation, the introduction rate is 4×six years (2×three years); and

- 2. at the Production phase, after the 4 Gbit generation, the introduction rate is 4×six years (2×three years).

§§ MPU Chip Size Model—Both the cost-performance and high-performance MPUs InTER-generation production-level chip sizes are modeled to be below affordable targets, which are flat through 2020 (280 mm²/cost-performance at introduction; 140 mm²/cost-performance at production; 310 mm²/high-performance at production). The MPU flat chip-size affordability model is accomplished by doubling the on-chip functionality every technology cycle. Actual market chip sizes may exceed the affordability targets in order to continue the doubling of on-chip functionality on a shorter cycle, but their unit costs and market values must be increased. In the 2005 ITRS, the MPU model now includes introduction-level high-performance MPU targets that shrink to the "affordable" targets (the same way the DRAM model operates). The InTRA-generation chip size shrink model is 0.5×every two-year density-driven technology cycle through 2004, and then 0.5×every three-year density-driven technology cycle after 2004, in order to stay under the affordable flat-chip-size target.

Refer to the Glossary for definitions.

# 電源と消費電力

いくつかの要因(消費電力の低下、トランジスタチャネル長の縮小、ゲート誘電体信頼性の向上)が電源電圧の低減(Table6a、6b 参照)を推し進めている。Table6a、6b に示すように、現在、電源電圧の値は範囲で与えられている。

特定の  $V_{dd}$ 値の選択は、1個の IC について速度と電力を同時に最適化する解析の一部として続けられており、各製品世代の使用可能電源電圧の範囲をもたらしている。高性能プロセッサーで 0.5V  $V_{dd}$  値は 2018 年までには達成されないだろう(2001 年版ITRSでは 2013 年で達成されると期待されていたが)。現在の  $V_{dd}$ 最低目標値は低消費電力応用製品で 2016 年に 0.5V となっており、(これは 2001 年版 IRTS の 0.6V 目標より低い値になっている。

最大電力傾向(MPU用)は3つのカテゴリで提示される。

- 1) 高性能デスクトップ・アプリケーション、パッケージのヒート・シンクを許容。

- 2) コスト重視型、最高性能の経済的な電力管理が最も重要。

- 3) 携帯電池運用(今や、アセンブリー・パッケージの TWG で「厳しい: Harsh」環境と名づけられている。)